### The Embedded I/O Company

# **TCP261**

### **Dual PMC Carrier for 6U CompactPCI (J3/J4 I/O)**

Version 1.0

### **User Manual**

Issue 1.3 June 2008

#### TCP261-10

Dual PMC Carrier for 6U CompactPCI with J3 and J4 I/O and 5V PMC V/IO voltage

#### TCP261-10

Dual PMC Carrier for 6U CompactPCI with J3 and J4 I/O and 3.3V PMC V/IO voltage

This document contains information, which is proprietary to TEWS TECHNOLOGIES GmbH. Any reproduction without written permission is forbidden.

TEWS TECHNOLOGIES GmbH has made any effort to ensure that this manual is accurate and complete. However TEWS TECHNOLOGIES GmbH reserves the right to change the product described in this document at any time without notice.

TEWS TECHNOLOGIES GmbH is not liable for any damage arising out of the application or use of the device described herein.

#### **Style Conventions**

Hexadecimal characters are specified with prefix 0x, i.e. 0x029E (that means hexadecimal value 029E).

For signals on hardware products, an ,Active Low' is represented by the signal name with # following, i.e. IP\_RESET#.

Access terms are described as:

W Write Only

R Read Only

R/W Read/Write

R/C Read/Clear

R/S Read/Set

©2005-2008 by TEWS TECHNOLOGIES GmbH

| Issue | Description                            | Date           |

|-------|----------------------------------------|----------------|

| 1.0   | Initial Issue                          | June 2005      |

| 1.1   | Correction Figure 7-4 (Compact PCI J4) | September 2005 |

| 1.2   | New address TEWS LLC                   | September 2006 |

| 1.3   | TCP261-11 board option added           | June 2008      |

## **Table of Contents**

| 1 | PRODUCT DESCRIPTION                                     | 6  |

|---|---------------------------------------------------------|----|

| 2 | TECHNICAL SPECIFICATION                                 | 7  |

| 3 | PCI TO PCI BRIDGE 21154                                 | 8  |

|   | 3.1 PCI Configuration Registers                         |    |

|   | 3.1.1 21154 PCI Header                                  |    |

|   | 3.2 Secondary Bus Device Number Mapping                 |    |

|   | 3.3 Local Register / Hot Swap Register                  |    |

|   | 3.3.1 GPIO Output Data Register – Offset 0x65           |    |

|   | 3.3.2 GPIO Output Enable Control Register – Offset 0x66 |    |

|   | 3.4 Secondary PCI Clock                                 |    |

|   | 3.4.1 Secondary PCI Clock Combinations                  |    |

|   | 3.4.2 Disabling Secondary PCI Clocks                    | 13 |

| 4 | PMC TO PCI INTERFACE                                    | 14 |

|   | 4.1 PMC BUSMODE[4:1] Signals                            |    |

|   | 4.2 Interrupt Routing                                   |    |

|   | 4.3 PCI Signaling Voltage                               | 15 |

|   | 4.3.1 Secondary PCI Bus PCI Signal Voltage Level        |    |

|   | 4.3.2 PCI Signaling Levels and Voltage Keying           |    |

| 5 | INSTALLATION OF A PMC MODULE                            | 18 |

| 6 | HOT SWAP                                                | 19 |

|   | 6.1 Insertion Process                                   | 19 |

|   | 6.2 Extraction Process                                  |    |

|   | 6.3 Non Hot Swap System                                 | 20 |

| 7 | PIN ASSIGNMENT                                          | 21 |

|   | 7.1 CompactPCI J1                                       |    |

|   | 7.2 CompactPCI J2                                       |    |

|   | 7.3 CompactPCI J3                                       |    |

|   | 7.4 CompactPCI J4                                       | 24 |

|   | 7.5 PMC J11 / P11 and J21 / P21                         | 25 |

|   | 7.6 PMC J12 / P12 and J22 / P22                         | _  |

|   | 7.7 PMC J13 / P13 and J23 / P23                         |    |

|   | 7.8 PMC .I14 / P14 and .I24 / P24                       | 28 |

## **Table of Figures**

| FIGURE 1-1 : BLOCK DIAGRAM                               | 6  |

|----------------------------------------------------------|----|

| FIGURE 2-1 : TECHNICAL SPECIFICATION                     | 7  |

| FIGURE 3-1 : 21154 PCI HEADER                            | 8  |

| FIGURE 3-2 : SECONDARY BUS DEVICE NUMBER MAPPING         | 9  |

| FIGURE 3-3 : HOT SWAP CONTROL AND STATUS REGISTER        | 10 |

| FIGURE 3-4 : GPIO OUTPUT DATA REGISTER                   | 11 |

| FIGURE 3-5 : GPIO OUTPUT ENABLE CONTROL REGISTER         | 11 |

| FIGURE 3-6 : GPIO INPUT DATA REGISTER                    | 11 |

| FIGURE 3-7 : SECONDARY PCI CLOCK COMBINATIONS            | 12 |

| FIGURE 3-8 : SECONDARY PCI CLOCK DISABLE JUMPER LOCATION | 13 |

| FIGURE 4-1 : INTERRUPT ROUTING                           | 14 |

| FIGURE 4-2 : PCI SIGNAL VOLTAGE CONFIGURATION RESISTORS  | 15 |

| FIGURE 4-3 : PMC VOLTAGE KEYING                          | 16 |

| FIGURE 4-4 : PCI SIGNAL VOLTAGE CONFIGURATION MATRIX     | 17 |

| FIGURE 5-1 : INSTALLATION OF A PMC MODULE                | 18 |

| FIGURE 6-1 : HOT SWAP CONTROL AND STATUS REGISTER        | 20 |

| FIGURE 7-1 : COMPACTPCI J1 PIN ASSIGNMENT                | 21 |

| FIGURE 7-2 : COMPACTPCI J2 PIN ASSIGNMENT                | 22 |

| FIGURE 7-3 : COMPACTPCI J3 PIN ASSIGNMENT                | 23 |

| FIGURE 7-4 : COMPACTPCI J4 PIN ASSIGNMENT                | 24 |

| FIGURE 7-5 : PMC J11/P11 AND J21/P21 PIN ASSIGNMENT      | 25 |

| FIGURE 7-6 : PMC J12/P12 AND J22/P22 PIN ASSIGNMENT      | 26 |

| FIGURE 7-7 : PMC J13/P13 AND J23/P23 PIN ASSIGNMENT      | 27 |

| FIGURE 7-8: PMC J14/P14 AND J24/P24 PIN ASSIGNMENT       | 28 |

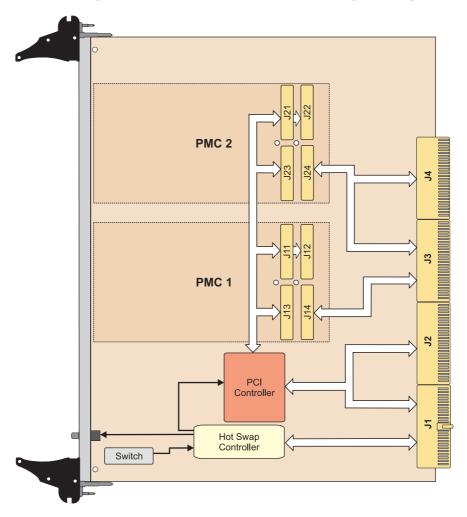

# 1 Product Description

The TCP261 is a standard 6U CompactPCI carrier that provides front I/O and rear I/O for up to two single width PMC modules.

The transparent Intel PCI-to-PCI bridge 21154 is used as the PCI bridging device between the primary CompactPCI bus and the on board secondary PCI bus where the two PMC slots reside.

Supported PCI bus data widths are 32 bit and 64 bit. Supported PCI bus frequencies are 33 MHz and 66 MHz.

The TCP261 supports standard PMC front I/O and CompactPCI rear I/O. The PMC slot 1 I/O lines are connected directly to the CompactPCI connector J3. The PMC slot 2 I/O lines are connected directly to the CompactPCI connector J3 and J4.

The TCP261 also provides hot swapping capability. The TCP261 on board hot swap controller controls the installation and reinstallation process of the TCP261 without powering down the CompactPCI system.

The TCP261 carrier complies with the PICMG 2.0 Revision 3.0 CompactPCI specification.

Figure 1-1: Block Diagram

# 2 Technical Specification

|                              | PCI Interface                                                                              |  |  |  |  |

|------------------------------|--------------------------------------------------------------------------------------------|--|--|--|--|

| CompactPCI Interface         | CompactPCI 6U, conforming to PICMG 2.0 R3.0                                                |  |  |  |  |

| PCI Interface                | PCI 2.2 compliant interface, 33 MHz/66 MHz, 32 bit/64 bit                                  |  |  |  |  |

| PCI I/O Signaling Voltage    | 3.3V or 5V (5V default) (configured by resistor placement)                                 |  |  |  |  |

| PCI to PCI Bridge            | Intel 21554                                                                                |  |  |  |  |

|                              | PMC Interface                                                                              |  |  |  |  |

| Number of PMC Slots          | 2                                                                                          |  |  |  |  |

| Supported PMC PCI Data Width | 32 bit/64 bit                                                                              |  |  |  |  |

| Supported PMC PCI Frequency  | 33 MHz/66 MHz                                                                              |  |  |  |  |

| PCI I/O Signaling Voltage    | TCP261-10: 5V V/IO voltage                                                                 |  |  |  |  |

|                              | TCP261-11: 3.3V V/IO voltage                                                               |  |  |  |  |

| PMC I/O Access               | Front panel I/O                                                                            |  |  |  |  |

|                              | P14/P24 Back I/O via CompactPCI J3/J4 connector                                            |  |  |  |  |

|                              | Physical Data                                                                              |  |  |  |  |

| Power Requirements           | 10 mA typical @ VI/O DC                                                                    |  |  |  |  |

| without PMC Modules plugged  | 80 mA typical @ +5V DC<br>100 mA typical @ +3.3V DC                                        |  |  |  |  |

| p.uggeu                      | 10 mA typical @ + 12V DC                                                                   |  |  |  |  |

|                              | <1 mA typical @ + 12V DC                                                                   |  |  |  |  |

|                              | Additional power is required by plugged PMC modules.                                       |  |  |  |  |

| Maximum Total Power for      | 5 A typical @ +5V DC                                                                       |  |  |  |  |

| both PMC Modules             | 5 A typical @ +3.3V DC                                                                     |  |  |  |  |

|                              | 1 A typical @ +12V DC                                                                      |  |  |  |  |

|                              | 1 A typical @ -12V DC                                                                      |  |  |  |  |

| Overcurrent Protection       | All four power supplies are disconnected from PMC modules during an overcurrent situation. |  |  |  |  |

| Temperature Range            | Operating 0°C to + 70°C                                                                    |  |  |  |  |

|                              | Storage -40°C to + 100°C                                                                   |  |  |  |  |

| MTBF                         | 225000 h                                                                                   |  |  |  |  |

| Weight                       | 302 g                                                                                      |  |  |  |  |

| Size                         | 160 mm x 233.35 mm                                                                         |  |  |  |  |

| Humidity                     | 5 – 95 % non- condensing                                                                   |  |  |  |  |

Figure 2-1: Technical Specification

# 3 PCI to PCI Bridge 21154

## 3.1 PCI Configuration Registers

#### 3.1.1 21154 PCI Header

| PCI CFG<br>Register | PCI Configuration Register                                         |                               |                                 |                           |           |

|---------------------|--------------------------------------------------------------------|-------------------------------|---------------------------------|---------------------------|-----------|

| Address             | 31 24                                                              | 23 16                         | 15 8                            | 7 0                       | writeable |

| 0x00                | Dev                                                                | ice ID                        | Vend                            | dor ID                    | N         |

| 0x04                | St                                                                 | atus                          | Com                             | mand                      | Υ         |

| 0x08                |                                                                    | Class Code                    |                                 | Revision ID               | N         |

| 0x0C                | Reserved                                                           | Header Type                   | Primary Latency<br>Timer        | Cache Line<br>Size        | Y[15:0]   |

| 0x10                |                                                                    | Res                           | erved                           |                           | N         |

| 0x14                |                                                                    | Res                           | erved                           |                           | N         |

| 0x18                | Secondary<br>Latency Timer                                         | Subordinate<br>Bus Number     | Secondary Bus<br>Number         | Primary Bus<br>Number     | Y         |

| 0x1C                | Seconda                                                            | ary Status                    | I/O Limit<br>Address            | I/O Base<br>Address       | Υ         |

| 0x20                | Memory L                                                           | mit Address                   | Memory Ba                       | ase Address               | Y         |

| 0x24                | Prefetchable Memory Limit Prefetchable Memory Base Address Address |                               | Y                               |                           |           |

| 0x28                | Prefet                                                             | chable Memory Ba              | ase Address Upper               | 32 Bits                   | Υ         |

| 0x2C                | Prefet                                                             | chable Memory Li              | mit Address Upper               | 32 Bits                   | Y         |

| 0x30                | I/O Limit Addre                                                    | ss Upper 16 Bits              | I/O Base Addre                  | ss Upper 16 Bits          | Y         |

| 0x34                |                                                                    | Reserved                      |                                 | ECP Pointer               | Υ         |

| 0x38                | Reserved                                                           |                               | erved                           |                           | N         |

| 0x3C                | Bridge                                                             | Control                       | Interrupt Pin                   | Reserved                  | Υ         |

| 0x40                | Arbiter Control                                                    |                               | Diagnostic Chip Control Control |                           | Y         |

| 0x44 - 0x60         |                                                                    | Res                           | erved                           |                           | N         |

| 0x64                | gpio Input Data                                                    | gpio Output<br>Enable Control | gpio Output<br>Data             | p_serr_l Event<br>Disable | Y         |

| 0x68                | Reserved                                                           | p_serr_l Status               | Secondary (                     | Clock Control             | Y         |

| 0x6C - 0xDB         | Reserved                                                           |                               |                                 |                           | N         |

| 0xDC                | Power Manage                                                       | ment Capabilities             | Nest Item Ptr. Capability ID    |                           | Y         |

| 0xE0                | Data                                                               | PPB Support<br>Extensions     | Power Management CSR            |                           | Υ         |

| 0xE4 – 0xFF         |                                                                    | Res                           | erved                           | N                         |           |

Figure 3-1: 21154 PCI Header

For further information please refer to the Intel PCI to PCI Bridge 21154 manual which is also part of the TCP261-ED Engineering Documentation.

## 3.2 Secondary Bus Device Number Mapping

The secondary bus device number of PMC slot 1 and PMC slot 2 is defined by configuration type translation of the Intel 21154 PCI to PCI Bridge.

By default PMC slot 1 is mapped to secondary bus device number 0x04, and PMC slot 2 is mapped to secondary bus device number 0x05.

| Secondary<br>Bus Device<br>Number<br>(HEX) | Secondary Bus AD(31:16)<br>(Binary)        | PCI AD<br>Line used<br>as PMC<br>IDSEL | Purpose                                           |

|--------------------------------------------|--------------------------------------------|----------------------------------------|---------------------------------------------------|

| 0<br>1                                     | 0000 0000 0000 0001<br>0000 0000 0000 0010 | 16<br>17                               | Implemented by 21154<br>but not used on<br>TCP261 |

| 2                                          | 0000 0000 0000 0100                        | 18                                     | Optional IDSEL for PMC1                           |

| 3                                          | 0000 0000 0000 1000                        | 19                                     | Optional IDSEL for PMC2                           |

| 4                                          | 0000 0000 0001 0000                        | 20                                     | Default IDSEL for PMC1                            |

| 5                                          | 0000 0000 0010 0000                        | 21                                     | Default IDSEL for PMC2                            |

| 6 -F                                       | 0000 0000 0100 0000<br>1000 0000 0000 0000 | 22 – 31                                | Implemented by 21154<br>but not used on<br>TCP261 |

| 10 – 1E                                    | 0000 0000 0000 0000                        | None                                   | Not implemented by 21154                          |

| 1F                                         | Special Cycle Data                         | -                                      | Special Cycles for PMC                            |

Figure 3-2: Secondary Bus Device Number Mapping

### 3.3 Local Register / Hot Swap Register

The 21154 PCI to PCI Bridge does not provide an internal Hot Swap control and status register for the direct control of Hot Swap installation and reinstallation process. Following the PICMG 2.1 R1.0 CompactPCI Hot Swap Specification, the TCP261 uses the alternate register implementation for the on board Hot Swap Register. Additional on board logic provides the required control and status information to handle the Hot Swap process.

The additional on board logic maps the four bits of the Hot Swap Register to the general purpose I/O lines of the 21154 PCI to PIC Bridge.

The TCP261 Hot Swap Registers is accessed using the 21154 GPIO registers in the 21154 PCI configuration register space.

To read the Hot Swap Register, the 21154 GPIO lines must first be configured as input only lines. This is done by setting up the GPIO Output Enable Control Register accordingly. Then the 21154 GPIO Input Data Register can be used to read the Hot Swap Register (after reset the 21154 GPIO lines are configured as inputs).

To write to the Hot Swap Register, the 21154 GPIO lines must first be configured as bi-directional I/O lines. This is done by setting up the GPIO Output Enable Control Register accordingly. Then the GPIO Output Data Register could be used to set or clear the bits in the Hot Swap Register.

| Bit /<br>GPIO | Symbol | Description                                                                                                         | Access | Reset<br>Value |

|---------------|--------|---------------------------------------------------------------------------------------------------------------------|--------|----------------|

| 0             | EIM    | Mask ENUM#                                                                                                          | R/W    | 0              |

|               |        | (d) Frankla FNI IM# sign                                                                                            |        |                |

|               |        | '1' – Enable ENUM# pin                                                                                              |        |                |

|               |        | '0' – Disable ENUM# pin                                                                                             |        |                |

| 1             | LOO    | Enable / Disable blue Hot Swap LED                                                                                  | R/W    | 0              |

|               |        |                                                                                                                     |        |                |

|               |        | '1' - Switch blue Hot Swap LED on                                                                                   |        |                |

|               |        | '0' - Switch blue Hot Swap LED off                                                                                  |        |                |

| 2             | EXT    | Pending Extraction of the TCP261                                                                                    | R/W    | 0              |

|               |        |                                                                                                                     |        |                |

|               |        | '1' - Indicates that the board is ready for extraction                                                              |        |                |

|               |        | '0' – Board is still installed                                                                                      |        |                |

|               |        | The systematical hit can be also used by continue (4) to the according                                              |        |                |

|               |        | The extraction bit can be cleared by writing '1' to the according bit. Setting the bit by software is not possible. |        |                |

| 3             | INS    | Freshly Inserted TCP261                                                                                             | R/W    | 1              |

|               |        |                                                                                                                     |        |                |

|               |        | '1' - Indicates that the TCP261 has been inserted                                                                   |        |                |

|               |        | '0' – No board changing                                                                                             |        |                |

|               |        |                                                                                                                     |        |                |

|               |        | The insertion bit can be cleared by writing '1' to the according bit.                                               |        |                |

|               |        | '0' – No board changing                                                                                             |        |                |

Figure 3-3: Hot Swap Control and Status Register

#### 3.3.1 GPIO Output Data Register – Offset 0x65

| Bit | Symbol | Description                                                                                                   | Access | Reset Value |

|-----|--------|---------------------------------------------------------------------------------------------------------------|--------|-------------|

| 0   | GPIO 0 | These four bits clear (setting to logical low level) the GPIO line by writing a '1' to the corresponding bit. | R/W    | "0000"      |

| 1   | GPIO 1 | Writing a (4) places the CDIO line                                                                            |        |             |

| 2   | GPIO 2 | Writing a '1' – clears the GPIO line Writing a '0' – no effect                                                |        |             |

| 3   | GPIO 3 | Reading reflects the last value written.                                                                      |        |             |

| 4   | GPIO 0 | These four bits set (setting to logical high level) the GPIO line by writing a '1' to the corresponding bit.  | R/W    | "0000"      |

| 5   | GPIO 1 | , , ,                                                                                                         |        |             |

| 6   | GPIO 2 | Writing a '1' – sets the GPIO line Writing a '0' – no effect                                                  |        |             |

| 7   | GPIO 3 | Reading reflects the last value written.                                                                      |        |             |

Figure 3-4: GPIO Output Data Register

#### 3.3.2 GPIO Output Enable Control Register - Offset 0x66

| Bit | Symbol | Description                                              | Access | Reset Value |

|-----|--------|----------------------------------------------------------|--------|-------------|

| 0   | GPIO 0 |                                                          | R/W    | "0000"      |

| 1   | GPIO 1 | Writing a '1' – sets the GPIO line mode to input only    |        |             |

| 2   | GPIO 2 | Writing a '0' – no effect                                |        |             |

| 3   | GPIO 3 | Reading reflects the last value written.                 |        |             |

| 4   | GPIO 0 |                                                          | R/W    | "0000"      |

| 5   | GPIO 1 | Writing a '0' - sets the GPIO line mode to bidirectional |        |             |

| 6   | GPIO 2 | Writing a '0' – no effect                                |        |             |

| 7   | GPIO 3 | Reading reflects the last value written.                 |        |             |

Figure 3-5: GPIO Output Enable Control Register

#### 3.3.3 GPIO Input Data Register – Offset 0x67

| Bit | Symbol   | Description                            | Access | Reset Value     |

|-----|----------|----------------------------------------|--------|-----------------|

| 3:0 | Reserved | Returns '0' on reads                   | R      | 0               |

| 4   | GPIO 0   | Reflects the Hot Swap Register bit 0 : | R      | Depends on GPIO |

| 5   | GPIO 1   | Reflects the Hot Swap Register bit 1 : |        | lines           |

| 6   | GPIO 2   | Reflects the Hot Swap Register bit 2 : |        |                 |

| 7   | GPIO 3   | Reflects the Hot Swap Register bit 3:  |        |                 |

Figure 3-6 : GPIO Input Data Register

For further information please refer to the Intel PCI to PCI Bridge 21154 manual which is also part of the TCP261-ED Engineering Documentation.

### 3.4 Secondary PCI Clock

#### 3.4.1 Secondary PCI Clock Combinations

For using 66 MHz PCI bus clock mode with the TCP261, the CompactPCI bus must support 66 MHz operation.

The secondary PCI bus on the TCP261 is configured by the plugged PMC modules. If any plugged PMC module does only support 33 MHz operation, the complete secondary PCI bus will always operate with 33 MHz only.

If the primary PCI bus does only support 33 MHz operation, the secondary PCI bus will also operate with 33 MHz only.

| Primary PCI Bus Frequency (CompactPCI Frequency) | PMC1 Frequency<br>Capability | PMC2 Frequency<br>Capability | Secondary PCI Bus<br>Operating Frequency<br>(PMC1 and PMC2<br>Frequency) |

|--------------------------------------------------|------------------------------|------------------------------|--------------------------------------------------------------------------|

| 33 MHz                                           | 33 MHz or 66 MHz             | 33 MHz or 66 MHz             | 33 MHz                                                                   |

| 66 MHz                                           | 33 MHz only                  | no PMC                       | 33 MHz                                                                   |

| 66 MHz                                           | no PMC                       | 33 MHz only                  | 33 MHz                                                                   |

| 66 MHz                                           | 33 MHz or 66 MHz             | 33 MHz only                  | 33 MHz                                                                   |

| 66 MHz                                           | 33 MHz only                  | 33 MHz or 66 MHz             | 33 MHz                                                                   |

| 66 MHz                                           | 33 MHz or 66 MHz             | no PMC                       | 66 MHz                                                                   |

| 66 MHz                                           | no PMC                       | 33 MHz or 66 MHz             | 66 MHz                                                                   |

| 66 MHz                                           | 33 MHz or 66 MHz             | 33 MHz or 66 MHz             | 66 MHz                                                                   |

Figure 3-7: Secondary PCI Clock Combinations

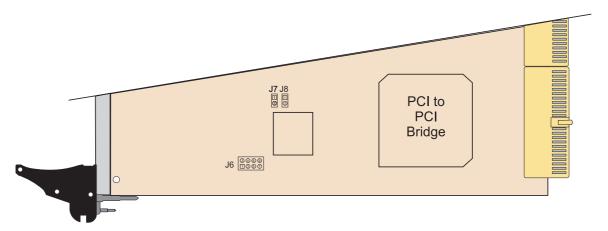

#### 3.4.2 Disabling Secondary PCI Clocks

The TCP261 always enables both PMC slot PCI clocks even if there is no PMC module plugged.

To disable the PCI clock for PMC slot 1 close Jumper J8.

To disable the PCI clock for PMC slot 2 close Jumper J7.

Figure 3-8: Secondary PCI Clock Disable Jumper Location

Closing the jumper disables the clock for the PMC slot even if there is a PMC module plugged.

## 4 PMC to PCI Interface

The TCP261 is a standard 6U CompactPCI carrier that provides front I/O and rear I/O for up to two single width PMC modules. The transparent Intel 21154 PCI to PCI Bridge provides the bridging between the primary CompactPCI bus and the secondary PCI bus where the two PMC slots reside.

### 4.1 PMC BUSMODE[4:1] Signals

The BUSMODE[4:1]# signals are unique to IEEE1386 (PMC) and are not found in the PCI or CompactPCI specification. They allow a host to identify the used mezzanine card type as a PMC card or as another existing mezzanine card type. The TCP261 does only support PMC cards. This "PMC only" configuration is indicated by pulling up BUSMODE2#, and pulling down BUSMODE3# and BUSMODE4#. The PMC card should decode the BUSMODE[4:2]# signals and drive out a logic "0" on BUSMODE1#.

### 4.2 Interrupt Routing

| Interrupt   | TCP261 –CompactPCI Pin Assignment | PMC 1<br>Device 4 | PMC 2<br>Device 5 |

|-------------|-----------------------------------|-------------------|-------------------|

| Interrupt A | INT A                             | INT A             | INT B             |

| Interrupt B | INT B                             | INT B             | INT C             |

| Interrupt C | INTC                              | INTC              | INT D             |

| Interrupt D | INT D                             | INT D             | INT A             |

Figure 4-1: Interrupt Routing

### 4.3 PCI Signaling Voltage

#### 4.3.1 Secondary PCI Bus PCI Signal Voltage Level

The secondary PCI bus signals connect to the 21154 PCI to PCI Bridge secondary PCI bus and to the PMC1 and PMC2 slots.

PMC modules are specified for 3.3V only, 5V only or universal (3.3V or 5V) PCI signal voltage operation.

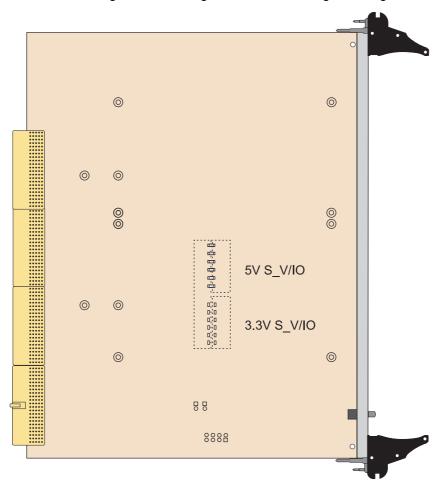

The TCP261 on board S\_V/IO signal voltage level defines the PCI signal voltage level for the TCP261 secondary PCI bus.

The TCP261-10 S\_V/IO voltage level is configured as 5V PCI signal voltage.

The TCP261-11 S\_V/IO voltage level is configured as 3.3V PCI signal voltage.

Figure 4-2: PCI Signal Voltage Configuration Resistors

The S\_V/IO signal voltage level is configured on board by resistor placement.

To switch the S\_V/IO voltage level between 3.3V PCI signal voltage and 5V PCI signal voltage, six SMD resistors on the bottom side of the TCP260 board must be swapped one location to the other location.

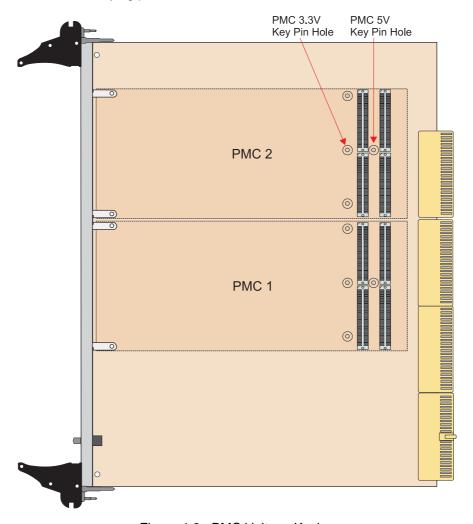

#### 4.3.2 PCI Signaling Levels and Voltage Keying

CompactPCI and PMC boards specify 5 Volt and 3.3 Volt PCI signaling voltage.

To prevent a PMC from being plugged into a PMC system with a different PCI signaling voltage, the PMC specification defines voltage keying by keying pins (on the PMC carrier board) and keying holes (on the PMC module).

PMC cards with only support of 5 Volt PCI signaling voltage provide a single keying hole for the 5 Volt keying pin. A 3.3 Volt only PMC provides only the keying hole for the 3.3 Volt keying pin. Universal PMC cards, which can handle 3.3 Volt and 5 Volt PCI signaling voltage, have keying holes for both voltage keying pins.

As factory default, the TCP261-10 is assembled with the 5 Volt keying pin on both PMC slots.

As factory default, the TCP261-11 is assembled with the 3.3 Volt keying pin on both PMC slots.

In certain system configurations it may be necessary to remove the keying pin from one location and assemble it at the other keying pin location.

Figure 4-3: PMC Voltage Keying

Use the following table to identify the required TCP261 Secondary PCI bus Configuration for the actual PMC modules that are to be used.

| PMC1<br>PCI Signal<br>Voltage<br>Capability | PMC2<br>PCI Signal<br>Voltage<br>Capability | TCP261 S_V/IO<br>Configuration | TCP261 5V<br>Keying Pin<br>Configuration | TCP261 3.3V<br>Keying Pin<br>Configuration |

|---------------------------------------------|---------------------------------------------|--------------------------------|------------------------------------------|--------------------------------------------|

| -                                           | -                                           | -                              | -                                        | -                                          |

| -                                           | 3.3V Only                                   | 3.3V                           | Not Installed                            | Installed                                  |

|                                             | 3.3V or 5V                                  | 3.3V                           | Not Installed                            | Installed                                  |

| -                                           | 3.30 01 30                                  | 5V                             | Installed                                | Not Installed                              |

| -                                           | 5V Only                                     | 5V                             | Installed                                | Not Installed                              |

| 3.3V Only                                   | -                                           | 3.3V                           | Not Installed                            | Installed                                  |

| 3.3V Only                                   | 3.3V Only                                   | 3.3V                           | Not Installed                            | Installed                                  |

| 3.3V Only                                   | 3.3V or 5V                                  | 3.3V                           | Not Installed                            | Installed                                  |

| 3.3V Only                                   | 5V Only                                     | -                              | -                                        | -                                          |

| 3.3V or 5V                                  |                                             | 3.3V                           | Not Installed                            | Installed                                  |

| 3.37 01 57                                  | -                                           | 5V                             | Installed                                | Not Installed                              |

| 3.3V or 5V                                  | 3.3V Only                                   | 3.3V                           | Not Installed                            | Installed                                  |

| 3.3V or 5V                                  | 3.3V or 5V                                  | 3.3V                           | Not Installed                            | Installed                                  |

| 3.30 01 50                                  | 3.30 01 50                                  | 5V                             | Installed                                | Not Installed                              |

| 3.3V or 5V                                  | 5V Only                                     | 5V                             | Installed                                | Not Installed                              |

| 5V Only                                     | -                                           | 5V                             | Installed                                | Not Installed                              |

| 5V Only                                     | 3.3V Only                                   | -                              | -                                        | -                                          |

| 5V Only                                     | 3.3V or 5V                                  | 5V                             | Installed                                | Not Installed                              |

| 5V Only                                     | 5V Only                                     | 5V                             | Installed                                | Not Installed                              |

Figure 4-4: PCI Signal Voltage Configuration Matrix

#### Factory default configuration is:

TCP261-10 TCP261-11

S\_V/IO Configuration: 5V 3.3V

5V Keying Pin: Installed Not Installed 3.3V Keying Pin: Not Installed Installed

#### WARNING !!!

Be sure that the TCP261 Secondary PCI bus Signal Voltage (S\_V/IO) configuration matches the TCP261 PMC slots keying pin configuration.

Be sure that the PMC modules that are to be used match to the TCP261 Secondary PCI bus Signal Voltage and PMC slot keying pin configuration.

If PMC modules are plugged into a PCI environment where the PCI signaling voltage does not match, damage to the equipment could occur, voiding product warranties.

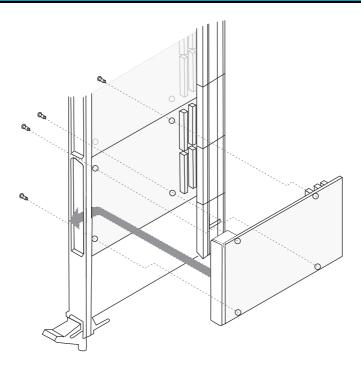

## 5 Installation of a PMC Module

Before installing a PMC module, be sure that the power supply for the TCP261 is turned off or the TCP261 is not installed into a CompactPCI system.

The components are Electrostatic Sensitive Devices (ESD). Use an anti-static mat connected to a wristband when handling or installing the components.

The PMC modules are mounted to the TCP261 prior to installation into the CompactPCI system.

If the PMC has a front panel, first remove the cover from the PMC front panel cut-out. Install the PMC at an angle so that the PMC front panel penetrates the PMC front panel cut-out. Then rotate down to mate with the PMC connectors on the TCP261. If the PMC has no front panel, simply plug in the PMC, and leave the cover in the PMC front panel cut-out.

After the PMC module has been installed, it can be mounted on the TCP261 using the mounting screws that come with the PMC module. There are four screw mounting locations, two at the PMC front panel and two at the standoffs near the PMC bus connectors.

#### **WARNING!!!**

Be sure that the TCP261 Secondary PCI bus Signal Voltage (S\_V/IO) configuration matches the TCP261 PMC slots keying pin configuration.

Be sure that the PMC modules that are to be used match to the TCP261 Secondary PCI bus Signal Voltage and PMC slot keying pin configuration.

If PMC modules are plugged into a PCI environment where the PCI signaling voltage does not match, damage to the equipment could occur, voiding product warranties.

Figure 5-1: Installation of a PMC Module

## 6 Hot Swap

#### **6.1 Insertion Process**

- Before inserting the TCP261 into a Hot Swap system the used PMC modules must be configured and mounted to the TCP261 PMC Slots.

- During insertion process the TCP261 front panel and board ground is de-charged by the ESD stripes and 10Mohm resistors to eliminate different voltage potentials between the TCP261 and the host system.

- The first CompactPCI connector pins that connect during the insertion process are the long power pins. These pins apply power to the PCI to PCI Bridge, the Hot Swap controller and the additional on board logic. The Hot Swap controller resets the PCI to PCI Bridge and precharges the on board PCI signal lines to 1V.

- The blue Hot Swap LED is switched on by hardware.

- The next pins which are connected are the medium length pins. The complete CompactPCI bus belongs to these pins.

- The last pin which is connected to the CompactPCI back plane is the BD\_SEL# pin. This line

indicates to the Hot Swap controller that all pins are connected and the power supplies for the

secondary PCI bus could be switched on.

- When the board is completely inserted and the insertion switch has locked, the INS bit in the Hot Swap Register is set, the ENUM# signal is asserted on the primary CompactPCI bus and the blue Hot Swap LED is switched off to signal not to extract the TCP261.

- The PCI to PCI Bridge can now be accessed (identified) on the primary CompactPCI bus.

- Upon detecting the asserted ENUM# signal, the CompactPCI host can now read the INS bit in the Hot Swap Register to determine if this is an insertion process. By clearing the INS bit, the CompactPCI host indicates to the TCP261 Hot Swap control logic that the host software has been configured.

#### **6.2 Extraction Process**

- When the micro-switch on the TCP261 handle is opened, the ENUM# signal is asserted on the CompactPCI bus and the EXT bit is set in the TCP261 Hot Swap Register.

- Upon detecting the asserted ENUM# signal, the host software can now read the EXT bit in the Hot Swap Register to determine if this is an extraction process.

- The host clears the EXT bit in the TCP261 Hot Swap Register to indicate that the host software has logged off the TCP261 from the CompactPCI bus.

- By switching on the blue Hot Swap LED via the TCP261 Hot Swap Register, the host system signals the user to go on with extraction process.

- Now the user is allowed to fully extract the TCP261.

For further information of Hot Swap please refer to the CompactPCI Hot Swap Specification PICMG 2.1 R2.0.

### 6.3 Non Hot Swap System

If the TCP261 is used in a non Hot Swap System the normal Hot Swap insertion process is dropped out. All PCI bus signals are already connected and be powered up by system control.

The TCP261 detects this normal start process and steps into a well know power on state. The blue Hot Swap LED is switched off by hardware to signal that the user is not allowed to extract the TCP261 from System.

The internal TCP261 Hot Swap state machine is set to state "insertion process completed" which means that the Hot Swap Register is set to the following value:

| Bit /<br>GPIO | Symbol | Description                                                                           | Power On value |

|---------------|--------|---------------------------------------------------------------------------------------|----------------|

| 0             | EIM    | '1' – Enable ENUM# pin<br>'0' – Disable ENUM# pin                                     | 0              |

| 1             | LOO    | '1' – Switch blue Hot Swap LED on '0' – Switch blue Hot Swap LED off                  | 0              |

| 2             | EXT    | '1' – Indicates that the board is ready for extraction '0' – Board is still installed | 0              |

| 3             | INS    | '1' – Indicates that the TCP261 has been inserted '0' – No board changing             | 1              |

Figure 6-1: Hot Swap Control and Status Register

In this state the PCI to PCI Bridge will work transparent without any Hot Swap device driver. All PCI configuration or data cycles are possible.

The same procedure is running if the TCP261 is still plugged in a Hot Swap system which is powered on or during a PCI bus reset.

# 7 Pin Assignment

## 7.1 CompactPCI J1

| Position | Row |          |         |            |          |          |

|----------|-----|----------|---------|------------|----------|----------|

| rosition | F   | E        | D       | С          | В        | Α        |

| 25       | GND | 5V       | 3.3V    | ENUM#      | REQ64#   | 5V       |

| 24       | GND | ACK64#   | AD[0]   | V(I/O) (L) | 5V       | AD[1]    |

| 23       | GND | AD[2]    | 5V (L)  | AD[3]      | AD[4]    | 3,3V     |

| 22       | GND | AD[5]    | AD[6]   | 3.3V (L)   | GND      | AD[7]    |

| 21       | GND | C/BE[0]# | M66EN   | AD[8]      | AD[9]    | 3,3V     |

| 20       | GND | AD[10]   | AD[11]  | V(I/O)     | GND      | AD[12]   |

| 19       | GND | AD[13]   | GND(L)  | AD[14]     | AD[15]   | 3,3V     |

| 18       | GND | C/BE[1]# | PAR     | 3.3V       | GND      | SERR#    |

| 17       | GND | PERR#    | GND (L) | IPMB_SDA   | IPMB_SCL | 3,3V     |

| 16       | GND | LOCK#    | STOP#   | V(I/O)     | GND      | DEVSEL#  |

| 15       | GND | TRDY#    | BD_SEL# | IRDY#      | FRAME#   | 3,3V     |

| 14       | GND | key      | key     | key        | key      | key      |

| 13       | GND | key      | key     | key        | key      | key      |

| 12       | GND | key      | key     | key        | key      | key      |

| 11       | GND | C/BE[2]# | GND (L) | AD[16]     | AD[17]   | AD[18]   |

| 10       | GND | AD[19]   | AD[20]  | 3.3V       | GND      | AD[21]   |

| 9        | GND | AD[22]   | GND (L) | AD[23]     | IDSEL    | C/BE[3]# |

| 8        | GND | AD[24]   | AD[25]  | V(I/O)     | GND      | AD[26]   |

| 7        | GND | AD[27]   | GND (L) | AD[28]     | AD[29]   | AD[30]   |

| 6        | GND | AD[31]   | CLK     | 3.3V (L)   | GND      | REQ#     |

| 5        | GND | GNT#     | GND (L) | RST#       | BRSVP1B5 | BRSVP1A5 |

| 4        | GND | INTS     | INTP    | V(I/O) (L) | HEALTHY# | IPMB_PWR |

| 3        | GND | INTD#    | 5V (L)  | INTC#      | INTB#    | INTA#    |

| 2        | GND | TDI      | TDO     | TMS        | 5V       | TCK      |

| 1        | GND | 5V       | +12V    | TRST#      | -12V     | 5V       |

Figure 7-1: CompactPCI J1 Pin Assignment

## 7.2 CompactPCI J2

| Desition | Row |          |          |          |          |          |

|----------|-----|----------|----------|----------|----------|----------|

| Position | F   | E        | D        | С        | В        | Α        |

| 22       | GND | NC       | NC       | NC       | NC       | NC       |

| 21       | GND | NC       | NC       | NC       | NC       | NC       |

| 20       | GND | NC       | NC       | NC       | NC       | NC       |

| 19       | GND | NC       | NC       | NC       | NC       | NC       |

| 18       | GND | NC       | NC       | NC       | NC       | NC       |

| 17       | GND | NC       | NC       | NC       | NC       | NC       |

| 16       | GND | NC       | NC       | NC       | NC       | NC       |

| 15       | GND | NC       | NC       | NC       | NC       | NC       |

| 14       | GND | AD[32]   | GND      | AD[33]   | AD[34]   | AD[35]   |

| 13       | GND | AD[36]   | AD[37]   | V(I/O)   | GND      | AD[38]   |

| 12       | GND | AD[39]   | GND      | AD[40]   | AD[41]   | AD[42]   |

| 11       | GND | AD[43]   | AD[44]   | V(I/O)   | GND      | AD[45]   |

| 10       | GND | AD[46]   | GND      | AD[47]   | AD[48]   | AD[49]   |

| 9        | GND | AD[50]   | AD[51]   | V(I/O)   | GND      | AD[52]   |

| 8        | GND | AD[53]   | GND      | AD[54]   | AD[55]   | AD[56]   |

| 7        | GND | AD[57]   | AD[58]   | V(I/O)   | GND      | AD[59]   |

| 6        | GND | AD[60]   | GND      | AD[61]   | AD[62]   | AD[63]   |

| 5        | GND | PAR64    | C/BE[4]# | V(I/O)   | EN64#    | C/BE[5]# |

| 4        | GND | C/BE[6]# | GND      | C/BE[7]# | BRSVP2B4 | V(I/O)   |

| 3        | GND | NC       | NC       | NC       | GND      | NC       |

| 2        | GND | NC       | NC       | NC       | NC       | NC       |

| 1        | GND | NC       | NC       | NC       | GND      | NC       |

Figure 7-2 : CompactPCI J2 Pin Assignment

## 7.3 CompactPCI J3

| Position | Row |             |             |             |             |             |

|----------|-----|-------------|-------------|-------------|-------------|-------------|

| Position | F   | E           | D           | С           | В           | Α           |

| 19       | GND | PMC2 I/O 41 | PMC2 I/O 42 | PMC2 I/O 43 | PMC2 I/O 44 | PMC2 I/O 45 |

| 18       | GND | PMC2 I/O 46 | PMC2 I/O 47 | PMC2 I/O 48 | PMC2 I/O 49 | PMC2 I/O 50 |

| 17       | GND | PMC2 I/O 51 | PMC2 I/O 52 | PMC2 I/O 53 | PMC2 I/O 54 | PMC2 I/O 55 |

| 16       | GND | PMC2 I/O 56 | PMC2 I/O 57 | PMC2 I/O 58 | PMC2 I/O 59 | PMC2 I/O 60 |

| 15       | GND | PMC2 I/O 61 | PMC2 I/O 62 | PMC2 I/O 63 | PMC2 I/O 64 | V I/O       |

| 14       | GND | 5V          | 5V          | 3,3V        | 3,3V        | 3,3V        |

| 13       | GND | PMC1 I/O 1  | PMC1 I/O 2  | PMC1 I/O 3  | PMC1 I/O 4  | PMC1 I/O 5  |

| 12       | GND | PMC1 I/O 6  | PMC1 I/O 7  | PMC1 I/O 8  | PMC1 I/O 9  | PMC1 I/O 10 |

| 11       | GND | PMC1 I/O 11 | PMC1 I/O 12 | PMC1 I/O 13 | PMC1 I/O 14 | PMC1 I/O 15 |

| 10       | GND | PMC1 I/O 16 | PMC1 I/O 17 | PMC1 I/O 18 | PMC1 I/O 19 | PMC1 I/O 20 |

| 9        | GND | PMC1 I/O 21 | PMC1 I/O 22 | PMC1 I/O 23 | PMC1 I/O 24 | PMC1 I/O 25 |

| 8        | GND | PMC1 I/O 26 | PMC1 I/O 27 | PMC1 I/O 28 | PMC1 I/O 29 | PMC1 I/O 30 |

| 7        | GND | PMC1 I/O 31 | PMC1 I/O 32 | PMC1 I/O 33 | PMC1 I/O 34 | PMC1 I/O 35 |

| 6        | GND | PMC1 I/O 36 | PMC1 I/O 37 | PMC1 I/O 38 | PMC1 I/O 39 | PMC1 I/O 40 |

| 5        | GND | PMC1 I/O 41 | PMC1 I/O 42 | PMC1 I/O 43 | PMC1 I/O 44 | PMC1 I/O 45 |

| 4        | GND | PMC1 I/O 46 | PMC1 I/O 47 | PMC1 I/O 48 | PMC1 I/O 49 | PMC1 I/O 50 |

| 3        | GND | PMC1 I/O 51 | PMC1 I/O 52 | PMC1 I/O 53 | PMC1 I/O 54 | PMC1 I/O 55 |

| 2        | GND | PMC1 I/O 56 | PMC1 I/O 57 | PMC1 I/O 58 | PMC1 I/O 59 | PMC1 I/O 60 |

| 1        | GND | PMC1 I/O 61 | PMC1 I/O 62 | PMC1 I/O 63 | PMC1 I/O 64 | V I/O       |

Figure 7-3: CompactPCI J3 Pin Assignment

## 7.4 CompactPCI J4

| Docition | Row |             |             |             |             |             |

|----------|-----|-------------|-------------|-------------|-------------|-------------|

| Position | F   | E           | D           | С           | В           | Α           |

| 25       | GND | NC          | NC          | NC          | NC          | NC          |

| 24       | GND | NC          | NC          | NC          | NC          | NC          |

| 23       | GND | NC          | NC          | NC          | NC          | NC          |

| 22       | GND | NC          | NC          | NC          | NC          | NC          |

| 21       | GND | NC          | NC          | NC          | NC          | NC          |

| 20       | GND | NC          | NC          | NC          | NC          | NC          |

| 19       | GND | NC          | NC          | NC          | NC          | NC          |

| 18       | GND | NC          | NC          | NC          | NC          | NC          |

| 17       | GND | NC          | NC          | NC          | NC          | NC          |

| 16       | GND | NC          | NC          | NC          | NC          | NC          |

| 15       | GND | NC          | NC          | NC          | NC          | NC          |

| 14       | GND |             |             |             |             |             |

| 13       | GND |             |             | Key Area    |             |             |

| 12       | GND |             |             |             |             |             |

| 11       | GND | NC          | NC          | NC          | NC          | NC          |

| 10       | GND | NC          | NC          | NC          | NC          | NC          |

| 9        | GND | GND         | GND         | GND         | GND         | GND         |

| 8        | GND | PMC2 I/O 1  | PMC2 I/O 2  | PMC2 I/O 3  | PMC2 I/O 4  | PMC2 I/O 5  |

| 7        | GND | PMC2 I/O 6  | PMC2 I/O 7  | PMC2 I/O 8  | PMC2 I/O 9  | PMC2 I/O 10 |

| 6        | GND | PMC2 I/O 11 | PMC2 I/O 12 | PMC2 I/O 13 | PMC2 I/O 14 | PMC2 I/O 15 |

| 5        | GND | PMC2 I/O 16 | PMC2 I/O 17 | PMC2 I/O 18 | PMC2 I/O 19 | PMC2 I/O 20 |

| 4        | GND | PMC2 I/O 21 | PMC2 I/O 22 | PMC2 I/O 23 | PMC2 I/O 24 | PMC2 I/O 25 |

| 3        | GND | PMC2 I/O 26 | PMC2 I/O 27 | PMC2 I/O 28 | PMC2 I/O 29 | PMC2 I/O 30 |

| 2        | GND | PMC2 I/O 31 | PMC2 I/O 32 | PMC2 I/O 33 | PMC2 I/O 34 | PMC2 I/O 35 |

| 1        | GND | PMC2 I/O 36 | PMC2 I/O 37 | PMC2 I/O 38 | PMC2 I/O 39 | PMC2 I/O 40 |

Figure 7-4 : CompactPCI J4 Pin Assignment

## 7.5 PMC J11 / P11 and J21 / P21

| Pin | Signal    | Signal   | Pin |

|-----|-----------|----------|-----|

| 1   | TCK       | -12V     | 2   |

| 3   | GND       | INTA#    | 4   |

| 5   | INTB#     | INTC#    | 6   |

| 7   | BUSMODE1# | +5V      | 8   |

| 9   | INTD#     | PCI-RSVD | 10  |

| 11  | GND       | 3.3Vaux  | 12  |

| 13  | CLK       | GND      | 14  |

| 15  | GND       | GNT#     | 16  |

| 17  | REG#      | +5V      | 18  |

| 19  | V (I/O)   | AD[31]   | 20  |

| 21  | AD[28]    | AD[27]   | 22  |

| 23  | AD[25]    | GND      | 24  |

| 25  | GND       | C/BE[3]# | 26  |

| 27  | AD[22]    | AD[21]   | 28  |

| 29  | AD[19]    | +5V      | 30  |

| 31  | V (I/O)   | AD[17]   | 32  |

| 33  | FRAME#    | GND      | 34  |

| 35  | GND       | IRDY#    | 36  |

| 37  | DEVSEL#   | +5V      | 38  |

| 39  | GND       | LOCK#    | 40  |

| 41  | PCI-RSVD  | PCI-RSVD | 42  |

| 43  | PAR       | GND      | 44  |

| 45  | V (I/O)   | AD[15]   | 46  |

| 47  | AD[12]    | AD[11]   | 48  |

| 49  | AD[09]    | +5V      | 50  |

| 51  | GND       | C/BE[0]# | 52  |

| 53  | AD[06]    | AD[05]   | 54  |

| 55  | AD[04]    | GND      | 56  |

| 57  | V (I/O)   | AD[03]   | 58  |

| 59  | AD[02]    | AD[01]   | 60  |

| 61  | AD[00]    | +5V      | 62  |

| 63  | GND       | REQ64#   | 64  |

Figure 7-5: PMC J11/P11 and J21/P21 Pin Assignment

### 7.6 PMC J12 / P12 and J22 / P22

| Pin | Signal    | Signal    | Pin |

|-----|-----------|-----------|-----|

| 1   | +12V      | TRST#     | 2   |

| 3   | TMS       | TDO       | 4   |

| 5   | TDI       | GND       | 6   |

| 7   | GND       | PCI-RSVD  | 8   |

| 9   | PCI-RSVD  | PCI-RSVD  | 10  |

| 11  | BUSMODE2# | +3.3V     | 12  |

| 13  | RST#      | BUSMODE3# | 14  |

| 15  | +3.3V     | BUSMODE4# | 16  |

| 17  | PME#      | GND       | 18  |

| 19  | AD[30]    | AD[29]    | 20  |

| 21  | GND       | AD[26]    | 22  |

| 23  | AD[24]    | +3.3V     | 24  |

| 25  | IDSEL     | AD[23]    | 26  |

| 27  | +3.3V     | AD[20]    | 28  |

| 29  | AD[18]    | GND       | 30  |

| 31  | AD[16]    | C/BE[2]#  | 32  |

| 33  | GND       | PMC-RSVD  | 34  |

| 35  | TRDY#     | +3.3V     | 36  |

| 37  | GND       | STOP#     | 38  |

| 39  | PERR#     | GND       | 40  |

| 41  | +3.3V     | SERR#     | 42  |

| 43  | C/BE[1]#  | GND       | 44  |

| 45  | AD[14]    | AD[13]    | 46  |

| 47  | M66EN     | AD[10]    | 48  |

| 49  | AD[08]    | +3.3V     | 50  |

| 51  | AD[07]    | PMC-RSVD  | 52  |

| 53  | +3.3V     | PMC-RSVD  | 54  |

| 55  | PMC-RSVD  | GND       | 56  |

| 57  | PMC-RSVD  | PMC-RSVD  | 58  |

| 59  | GND       | PMC-RSVD  | 60  |

| 61  | ACK64#    | +3.3V     | 62  |

| 63  | GND       | PMC-RSVD  | 64  |

Figure 7-6: PMC J12/P12 and J22/P22 Pin Assignment

## 7.7 PMC J13 / P13 and J23 / P23

| Pin | Signal   | Signal   | Pin |

|-----|----------|----------|-----|

| 1   | PCI-RSVD | GND      | 2   |

| 3   | GND      | C/BE[7]# | 4   |

| 5   | C/BE[6]# | C/BE[5]# | 6   |

| 7   | C/BE[5]# | GND      | 8   |

| 9   | V(I/O)   | PAR64    | 10  |

| 11  | AD[63]   | AD[62]   | 12  |

| 13  | AD[61]   | GND      | 14  |

| 15  | GND      | AD[60]   | 16  |

| 17  | AD[59]   | AD[58]   | 18  |

| 19  | AD[57]   | GND      | 20  |

| 21  | V(I/O)   | AD[56]   | 22  |

| 23  | AD[55]   | AD[54]   | 24  |

| 25  | AD[53]   | GND      | 26  |

| 27  | GND      | AD[52]   | 28  |

| 29  | AD[51]   | AD[50]   | 30  |

| 31  | AD[49]   | GND      | 32  |

| 33  | GND      | AD[48]   | 34  |

| 35  | AD[47]   | AD[46]   | 36  |

| 37  | AD[45]   | GND      | 38  |

| 39  | V(I/O)   | AD[44]   | 40  |

| 41  | AD[43]   | AD[42]   | 42  |

| 43  | AD[41]   | GND      | 44  |

| 45  | GND      | AD[40]   | 46  |

| 47  | AD[39]   | AD[38]   | 48  |

| 49  | AD[37]   | GND      | 50  |

| 51  | GND      | AD[36]   | 52  |

| 53  | AD[35]   | AD[34]   | 54  |

| 55  | AD[33]   | GND      | 56  |

| 57  | V(I/O)   | AD[32]   | 58  |

| 59  | PCI-RSVD | PCI_RSVD | 60  |

| 61  | PCI-RSVD | GND      | 62  |

| 63  | GND      | PCI-RSVD | 64  |

Figure 7-7: PMC J13/P13 and J23/P23 Pin Assignment

## 7.8 PMC J14 / P14 and J24 / P24

| Pin | Signal | Signal | Pin |

|-----|--------|--------|-----|

| 1   | I/O 1  | I/O 2  | 2   |

| 3   | I/O 3  | I/O 4  | 4   |

| 5   | I/O 5  | I/O 6  | 6   |

| 7   | I/O 7  | I/O 8  | 8   |

| 9   | I/O 9  | I/O 10 | 10  |

| 11  | I/O 11 | I/O 12 | 12  |

| 13  | I/O 13 | I/O 14 | 14  |

| 15  | I/O 15 | I/O 16 | 16  |

| 17  | I/O 17 | I/O 18 | 18  |

| 19  | I/O 19 | I/O 20 | 20  |

| 21  | I/O 21 | I/O 22 | 22  |

| 23  | I/O 23 | I/O 24 | 24  |

| 25  | I/O 25 | I/O 26 | 26  |

| 27  | I/O 27 | I/O 28 | 28  |

| 29  | I/O 29 | I/O 30 | 30  |

| 31  | I/O 31 | I/O 32 | 32  |

| 33  | I/O 33 | I/O 34 | 34  |

| 35  | I/O 35 | I/O 36 | 36  |

| 37  | I/O 37 | I/O 38 | 38  |

| 39  | I/O 39 | I/O 40 | 40  |

| 41  | I/O 41 | I/O 42 | 42  |

| 43  | I/O 43 | I/O 44 | 44  |

| 45  | I/O 45 | I/O 46 | 46  |

| 47  | I/O 47 | I/O 48 | 48  |

| 49  | I/O 49 | I/O 50 | 50  |

| 51  | I/O 51 | I/O 52 | 52  |

| 53  | I/O 53 | I/O 54 | 54  |

| 55  | I/O 55 | I/O 56 | 56  |

| 57  | I/O 57 | I/O 58 | 58  |

| 59  | I/O 59 | I/O 60 | 60  |

| 61  | I/O 61 | I/O 62 | 62  |

| 63  | I/O 63 | I/O 64 | 64  |

Figure 7-8: PMC J14/P14 and J24/P24 Pin Assignment