# **TPMC501**

# **Optically Isolated 32 Channel 16 Bit ADC**

Version 1.1

# **User Manual**

Issue 1.1.12 January 2010

#### TEWS TECHNOLOGIES GmbH

Am Bahnhof 7

25469 Halstenbek, Germany

Phone: +49 (0) 4101 4058 0

Fax: +49 (0) 4101 4058 19

e-mail: info@tews.com

www.tews.com

#### **TPMC501-10**

32 single-ended or 16 differential channels of isolated 16 bit ADC, gain 1, 2, 5, 10 input range +/-10V with front panel I/O

#### **TPMC501-11**

32 single-ended or 16 differential channels of isolated 16 bit ADC, gain 1, 2, 4, 8 input range +/-10V with front panel I/O

#### **TPMC501-12**

32 single-ended or 16 differential channels of isolated 16 bit ADC, gain 1, 2, 5, 10 input range 0V to 10V with front panel I/O

#### **TPMC501-13**

32 single-ended or 16 differential channels of isolated 16 bit ADC, gain 1, 2, 4, 8 input range 0V to 10V with front panel I/O

#### **TPMC501-20**

32 single-ended or 16 differential channels of isolated 16 bit ADC, gain 1, 2, 5, 10 input range +/-10V with P14 I/O

#### **TPMC501-21**

32 single-ended or 16 differential channels of isolated 16 bit ADC, gain 1, 2, 4, 8 input range +/-10V with P14 I/O

#### **TPMC501-22**

32 single-ended or 16 differential channels of isolated 16 bit ADC, gain 1, 2, 5, 10 input range 0V to 10V with P14 I/O

#### **TPMC501-23**

32 single-ended or 16 differential channels of isolated 16 bit ADC, gain 1, 2, 4, 8 input range 0V to 10V with P14 I/O

This document contains information, which is proprietary to TEWS TECHNOLOGIES GmbH. Any reproduction without written permission is forbidden.

TEWS TECHNOLOGIES GmbH has made any effort to ensure that this manual is accurate and complete. However TEWS TECHNOLOGIES GmbH reserves the right to change the product described in this document at any time without notice.

TEWS TECHNOLOGIES GmbH is not liable for any damage arising out of the application or use of the device described herein.

#### Style Conventions

Hexadecimal characters are specified with prefix 0x, i.e. 0x029E (that means hexadecimal value 029E).

For signals on hardware products, an ,Active Low' is represented by the signal name with # following, i.e. IP\_RESET#.

Access terms are described as:

| W   | Write Only |

|-----|------------|

| R   | Read Only  |

| R/W | Read/Write |

| R/C | Read/Clear |

| R/S | Read/Set   |

|     |            |

#### ©1999-2010 by TEWS TECHNOLOGIES GmbH

All trademarks mentioned are property of their respective owners.

| Issue  | Description                                         | Date           |

|--------|-----------------------------------------------------|----------------|

|        | Preliminary Issue                                   | January 1999   |

| 1.0    | First Issue                                         | April 1999     |

| 1.1    | Revision of Technical Specification                 | March 2000     |

| 1.2    | Revision of Interrupt Status Register               | June 2000      |

| 1.3    | Revision of Technical Specification                 | February 2001  |

| 1.4    | General Revision                                    | November 2002  |

| 1.5    | Technical Specification Table corrected             | November 2002  |

| 1.6    | Technical Specification Table corrected             | December 2003  |

| 1.7    | Added note for ADC conversion and Installation Note | October 2004   |

| 1.8    | New address TEWS LLC                                | September 2006 |

| 1.9    | New Hardware Version                                | April 2008     |

| 1.1.10 | New notation of User Manual Issue                   | February 2009  |

| 1.1.11 | Corrected PCI BAR number in 3.3 Note                | October 2009   |

| 1.1.12 | Added Analog Input Impedance                        | January 2010   |

## **Table of Contents**

| 1 | PRODUCT DESCRIPTION                                                                                                           | 6  |

|---|-------------------------------------------------------------------------------------------------------------------------------|----|

| 2 | TECHNICAL SPECIFICATION                                                                                                       | 7  |

| 3 | LOCAL SPACE ADDRESSING                                                                                                        | 9  |

|   | 3.1 PCI9030 Local Space Configuration                                                                                         | 9  |

|   | 3.2 Local Register Address Space                                                                                              | 10 |

|   | 3.2.1 ADC Control Register CONTREG (Offset 0x00)                                                                              |    |

|   | 3.2.2 ADC Data Register DATAREG (Offset 0x02)                                                                                 |    |

|   | <ul> <li>3.2.3 ADC Status Register STATREG (Offset 0x04)</li> <li>3.2.4 ADC Convert Register CONVERT (Offset 0x06)</li> </ul> |    |

|   | 3.2.5 Interrupt Status Register INTSTAT (Offset 0x08)                                                                         |    |

|   | 3.2.6 Sequencer Control Register SEQCONT (Offset 0x0A)                                                                        |    |

|   | 3.2.7 Sequencer Status Register SEQSTAT (Offset 0x0C)                                                                         |    |

|   | 3.2.8 Sequencer Timer Register SEQTIMER (Offset 0x0E)                                                                         |    |

|   | 3.2.9 Sequencer Instruction RAM SIRAM0-31 (Offset 0x80 to 0xBE)                                                               |    |

|   | <ul><li>3.2.10 Sequencer Data RAM SDRAM0-31 (Offset 0xC0 to 0xFE)</li><li>3.3 Calibration Data ROM Space</li></ul>            |    |

|   | 3.3.1 Data Correction                                                                                                         |    |

|   | 3.3.2 ADC Data Correction Formula                                                                                             |    |

| 4 | PCI9030 TARGET CHIP                                                                                                           |    |

| - | 4.1 PCI Configuration Registers (PCR)                                                                                         |    |

|   | 4.1.1 PCI9030 Header                                                                                                          |    |

|   | 4.2 Local Configuration Register (LCR)                                                                                        |    |

|   | 4.3 Configuration EEPROM                                                                                                      |    |

|   | 4.4 Local Software Reset                                                                                                      |    |

| 5 | OPERATION MODES                                                                                                               | 27 |

|   | 5.1 Conventional Modes                                                                                                        | 27 |

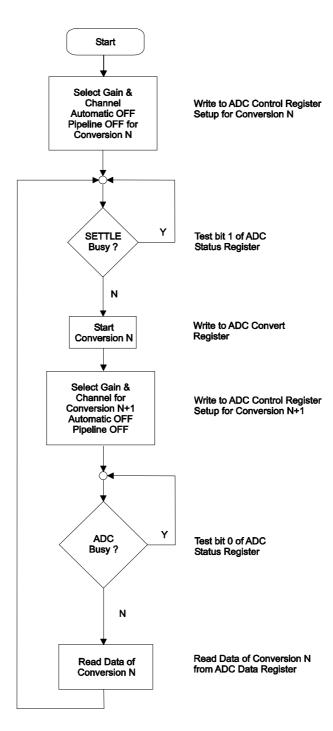

|   | 5.1.1 Normal Mode                                                                                                             | 28 |

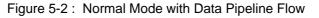

|   | 5.1.1.1 Normal Mode without Data Pipeline                                                                                     |    |

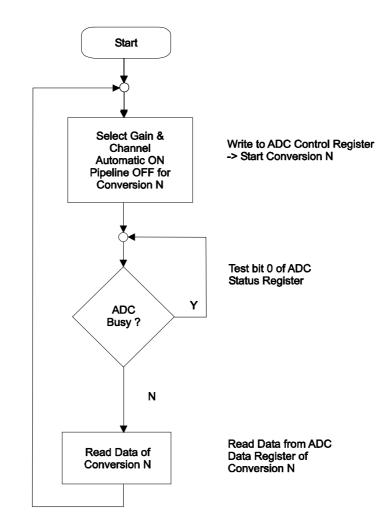

|   | 5.1.1.2 Normal Mode with Data Pipeline                                                                                        |    |

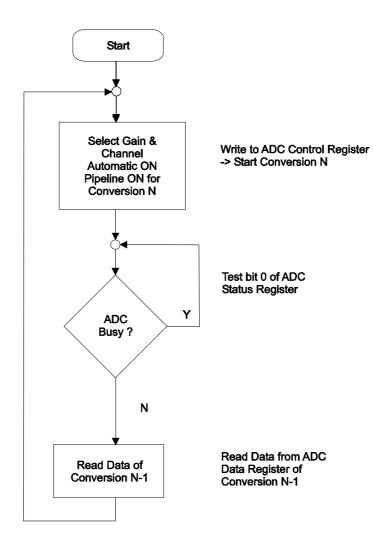

|   | 5.1.2 Automatic Mode<br>5.1.2.1 Automatic Mode without Data Pipeline                                                          |    |

|   | 5.1.2.2 Automatic Mode with Data Pipeline                                                                                     |    |

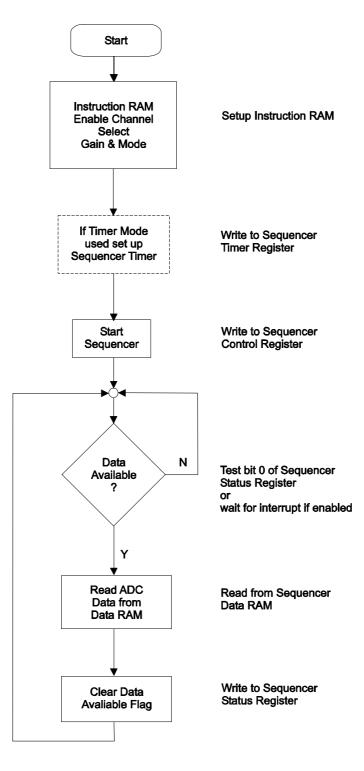

|   | 5.2 Sequencer Mode                                                                                                            |    |

|   | 5.2.1 Sequencer Errors                                                                                                        | 35 |

|   | 5.2.2 Sequencer Mode Flow                                                                                                     | 36 |

| 6 | PIN ASSIGNMENT                                                                                                                |    |

|   | 6.1 Pin Assignment HD50 Connector / P14 I/O                                                                                   | 37 |

| 7 | PROGRAMMING NOTE                                                                                                              | 39 |

| 8 | INSTALLATION NOTE                                                                                                             | 40 |

# List of Figures

|                                                           | -  |

|-----------------------------------------------------------|----|

| FIGURE 3-1: SEQUENCER TIMER VALUE                         | 1  |

| FIGURE 3-2: ADC CORRECTION FORMULA (BIPOLAR INPUT RANGE)  | 22 |

| FIGURE 3-3: ADC CORRECTION FORMULA (UNIPOLAR INPUT RANGE) | 22 |

| FIGURE 5-1: NORMAL MODE WITHOUT DATA PIPELINE FLOW        | 29 |

| FIGURE 5-2 : NORMAL MODE WITH DATA PIPELINE FLOW          | 30 |

| FIGURE 5-3 : AUTOMATIC MODE WITHOUT DATA PIPELINE FLOW    | 32 |

| FIGURE 5-4 : AUTOMATIC MODE WITH DATA PIPELINE FLOW       | 33 |

| FIGURE 5-5 : SEQUENCER MODE FLOW                          | 36 |

## **List of Tables**

| TABLE 2-1 : TECHNICAL SPECIFICATION               | 8  |

|---------------------------------------------------|----|

|                                                   |    |

| TABLE 3-1 : PCI9030 LOCAL SPACE CONFIGURATION     | 9  |

| TABLE 3-2 : LOCAL REGISTER ADDRESS SPACE1         | 0  |

| TABLE 3-3 : ADC CONTROL REGISTER CONTREG1         |    |

| TABLE 3-4 : 16 BIT ADC DATA REGISTER DATAREG1     | 3  |

| TABLE 3-5 : ADC DATA CODING1                      | 3  |

| TABLE 3-6 : ADC STATUS REGISTER STATREG1          | 4  |

| TABLE 3-7 : INTERRUPT STATUS REGISTER INTSTAT1    | 5  |

| TABLE 3-8 : SEQUENCER CONTROL REGISTER SEQCONT    |    |

| TABLE 3-9 : SEQUENCER STATUS REGISTER SEQSTAT1    | 6  |

| TABLE 3-10: SEQUENCER INSTRUCTION RAM SIRAM0-311  | 8  |

| TABLE 3-11: SEQUENCER INSTRUCTION WORD            | 9  |

| TABLE 3-12: SEQUENCER DATA RAM SDRAM0-31          | 20 |

| TABLE 3-13: CALIBRATION DATA VALUES               |    |

| TABLE 4-1 : PCI9030 HEADER                        | :3 |

| TABLE 4-2 : PCI9030 LOCAL CONFIGURATION REGISTERS | :4 |

| TABLE 4-3 : CONFIGURATION EEPROM TPMC501-XX2      | :5 |

| TABLE 5-1 : CONVENTIONAL OPERATING MODES          |    |

| TABLE 5-2 : SEQUENCER ERRORS                      | 5  |

| TABLE 6-1 : I/O PIN ASSIGNMENT                    | 8  |

# 1 **Product Description**

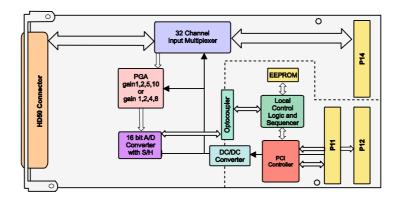

The TPMC501 is a PCI Mezzanine Card providing 32 galvanically isolated multiplexed 16 bit ADC channels.

The ADC channels can be software configured to operate in single-ended mode (up to 32 channels) or differential mode (up to 16 channels). Mixed mode configuration is possible.

The analog inputs are overvoltage protected for up to 70 Vpp.

A programmable gain amplifier allows various input voltage ranges.

| Board Option | I/O Connection | Gain Factors | Input Voltage Range      |

|--------------|----------------|--------------|--------------------------|

| TPMC501-10   | HD50 Front     | 1, 2, 5, 10  | $\pm 10V$ for gain = 1   |

| TPMC501-11   | HD50 Front     | 1, 2, 4, 8   | $\pm 10V$ for gain = 1   |

| TPMC501-12   | HD50 Front     | 1, 2, 5, 10  | 0V to $10V$ for gain = 1 |

| TPMC501-13   | HD50 Front     | 1, 2, 4, 8   | 0V to $10V$ for gain = 1 |

| TPMC501-20   | P14 Back       | 1, 2, 5, 10  | $\pm 10V$ for gain = 1   |

| TPMC501-21   | P14 Back       | 1, 2, 4, 8   | $\pm 10V$ for gain = 1   |

| TPMC501-22   | P14 Back       | 1, 2, 5, 10  | 0V to $10V$ for gain = 1 |

| TPMC501-23   | P14 Back       | 1, 2, 4, 8   | 0V to 10V for gain = 1   |

Table 1-1 : Board Option Overview

Data acquisition and conversion time is mode-dependent. Fastest acquisition and conversion time is 12µs without channel / gain change, 14.5µs with channel / gain change.

The TPMC501 provides a "Sequencer Mode" where the enabled ADC channels can be sampled at a fix rate. For each sequence the ADC data for all enabled channels is stored in a sequencer data RAM.

The repeat frequency of the sequencer can be programmed by using a sequencer timer. The sequencer timer is programmable from  $100\mu$ s to 6.5535s in steps of  $100\mu$ s. A special function is the "Sequencer Continuous Mode". In this mode the sequencer will start a new sequence immediately when a sequence is done.

Each TPMC501 is factory calibrated. The calibration data for each gain is stored in an EEPROM unique to each TPMC501. The modules accuracy is increased by performing data correction in software using the board calibration data values.

Figure 1-1 : Block Diagram

# 2 **Technical Specification**

|                           | Logic Interface                                                                                                               |                                                                    |  |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--|

| Mechanical Interface      | PCI Mezzanine Card Interface                                                                                                  | e (single size)                                                    |  |

| Electrical Interface      | PCI Rev. 2.2 compliant                                                                                                        |                                                                    |  |

|                           | 33 MHz / 32 bit PCI                                                                                                           |                                                                    |  |

|                           | 3.3V and 5V PCI Signaling Vo                                                                                                  | oltage                                                             |  |

|                           | On Board Devices                                                                                                              |                                                                    |  |

| PCI Target Chip           | PCI9030 (PLX Technology)                                                                                                      |                                                                    |  |

| ADC                       | ADS7809 (Texas Instruments                                                                                                    | 3)                                                                 |  |

| PGA                       | PGA206 / 207 (Texas Instrum                                                                                                   | nents)                                                             |  |

|                           | I/O Interface                                                                                                                 |                                                                    |  |

| I/O Interface             | TPMC501-1x : HD50 female of TPMC501-2x : P14 PMC Cor                                                                          |                                                                    |  |

| Number of Analog Channels | 32 single-ended channels or mixed mode is possible                                                                            | 16 differential channels,                                          |  |

| Input Impedance           | Typically $10^{12} \Omega$ (4nA leakage                                                                                       | e current)                                                         |  |

| Input Isolation           | The analog part (Analog input path and ADC device) is galvanically isolated from the PMC Interface. (1000V isolation voltage) |                                                                    |  |

| Input Isolation           | The analog part (Analog input path and ADC device) is galvanically isolated from the PMC Interface. (1000V isolation voltage) |                                                                    |  |

| Input Gain Amplifier      | TPMC501-10 / -20, -12 / -22 :                                                                                                 |                                                                    |  |

|                           | Programmable for gain 1, 2, 5                                                                                                 | 5, 10                                                              |  |

|                           | TPMC501-11/-21, -13/-23:                                                                                                      |                                                                    |  |

|                           | Programmable for gain 1, 2, 4, 8                                                                                              |                                                                    |  |

| Input Voltage Range       | <u>TPMC501-10 / -20 :</u>                                                                                                     | <u>TPMC501-12 / -22 :</u>                                          |  |

|                           | ±10V (gain = 1)                                                                                                               | 0V to $10V$ (gain = 1)                                             |  |

|                           | ±5V (gain = 2)                                                                                                                | 0V to $5V$ (gain = 2)                                              |  |

|                           | ±2V (gain = 5)                                                                                                                | 0V to 2V (gain = 5)                                                |  |

|                           | ±1V (gain = 10)                                                                                                               | 0V to 1V (gain = 10)                                               |  |

|                           |                                                                                                                               | TDMC501 42 / 02 .                                                  |  |

|                           | <u>TPMC501-11 / -21 :</u>                                                                                                     | $\frac{\text{TPMC501-13} / -23:}{0 \times 10 \times 10 \times 10}$ |  |

|                           | $\pm 10V$ (gain = 1)                                                                                                          | 0V  to  10V  (gain = 1)                                            |  |

|                           | $\pm 5V (gain = 2)$ 0V to 5V (gain = 2)                                                                                       |                                                                    |  |

|                           | $\pm 2.5V$ (gain = 4) 0V to 2.5V (gain = 4)                                                                                   |                                                                    |  |

|                           | $\pm 1.25V$ (gain = 8) 0V to 1.25V (gain = 8)                                                                                 |                                                                    |  |

| Input Overvoltage         | Protection for up to 70Vpp                                                                                                    |                                                                    |  |

| Input MUX Leakage Current | typical 4nA                                                                                                                   |                                                                    |  |

| Input PGA Impedance       | typical 10 <sup>13</sup> Ohm    1pF                                                                                           |                                                                    |  |

| Input ADC                 | 16 bit ADC                                                                                                                    |                                                                    |  |

| Data acquisition and conversion time up to 12µs without channel / gain change and up to 14.5µs with channel / gain change (mode-dependent) |

|--------------------------------------------------------------------------------------------------------------------------------------------|

| gain change (mode-dependent)                                                                                                               |

| Conversion Time with Gain /<br>Channel Change | Normal Mode with Data Pipeline: 14.5µs<br>Normal Mode without Data Pipeline: 22.5µs |  |  |

|-----------------------------------------------|-------------------------------------------------------------------------------------|--|--|

| channel change                                |                                                                                     |  |  |

|                                               | Automatic Mode with Data Pipeline: 22.5µs                                           |  |  |

|                                               | Automatic Mode without Data Pipeline: 32.5µs                                        |  |  |

| Calibration Data                              | Gain and offset factors stored in on board EEPROM                                   |  |  |

| Sequencer                                     | Optional Sequencer Mode                                                             |  |  |

|                                               | 4 bit Instruction RAM for each channel                                              |  |  |

|                                               | 2x16 bit Data RAM for each channel                                                  |  |  |

|                                               | Continuous Mode : 12µs + 14.5µs per channel                                         |  |  |

|                                               | Timer Mode : 100µs to 6.5535s (100µs steps)                                         |  |  |

| Accuracy                                      | $\pm$ 4 LSB after calibration for all TPMC501 modules                               |  |  |

| Linearity                                     | $\pm$ 4 LSB for all TPMC501 modules                                                 |  |  |

| ADC INL/DNL Error                             | $\pm$ 2 LSB for INL and DNL                                                         |  |  |

|                                               | Physical Data                                                                       |  |  |

| Power Requirements                            | 300mA typical @+5V                                                                  |  |  |

|                                               | 120mA typical @+3.3V                                                                |  |  |

| Temperature Range                             | Operating -40°C to +85°C                                                            |  |  |

|                                               | Storage -40°C to +125°C                                                             |  |  |

| Humidity                                      | 5 – 95% non-condensing                                                              |  |  |

| Weight                                        | TPMC501-1x : 78g                                                                    |  |  |

|                                               | TPMC501-2x : 63g                                                                    |  |  |

| MTBF                                          | TPMC501-1x : 552000 h                                                               |  |  |

|                                               | TPMC501-2x : 578000 h                                                               |  |  |

|                                               |                                                                                     |  |  |

Table 2-1 : Technical Specification

# 3 Local Space Addressing

## 3.1 PCI9030 Local Space Configuration

The local on board addressable regions are accessed from the PCI side by using the PCI9030 local spaces.

| PCI9030<br>Local<br>Space | PCI9030<br>PCI Base Address<br>(Offset in PCI<br>Configuration<br>Space) | PCI<br>Space<br>Mapping | Size<br>(Byte) | Port<br>Width<br>(Bit) | Endian<br>Mode | Description      |

|---------------------------|--------------------------------------------------------------------------|-------------------------|----------------|------------------------|----------------|------------------|

| 0                         | 2 (0x18)                                                                 | I/O                     | 256            | 16                     | BIG            | Local Register   |

| 1                         | 3 (0x1C)                                                                 | MEM                     | 2K             | 8                      | BIG            | Calibration Data |

| 2                         | 4 (0x20)                                                                 | -                       | -              | -                      | -              | Not Used         |

| 3                         | 5 (0x24)                                                                 | -                       | -              | -                      | -              | Not Used         |

Table 3-1 : PCI9030 Local Space Configuration

## 3.2 Local Register Address Space

PCI Base Address: PCI9030 PCI Base Address 2 (Offset 0x18 in PCI Configuration Space).

The TPMC501 is controlled by a set of 8 registers, located in the local register address space. All registers are cleared to '0' on power up or PCI reset.

Registers CONTREG, DATAREG, STATREG, CONVERT are used for conventional mode (non sequencer mode).

Registers SEQCONT, SEQSTAT, SEQTIMER are used for "Sequencer Mode".

The sequencer instruction and data RAM are also located in this local register address space.

| Offset to PCI<br>Base Address | Register  | Description Size<br>(Bit)     |    | Access |

|-------------------------------|-----------|-------------------------------|----|--------|

| 0x00                          | CONTREG   | ADC Control Register          | 16 | R/W    |

| 0x02                          | DATAREG   | ADC Data Register             | 16 | R      |

| 0x04                          | STATREG   | ADC Status Register           | 16 | R      |

| 0x06                          | CONVERT   | ADC Convert Start Register    | 16 | W      |

| 0x08                          | INTSTAT   | ADC Interrupt Status Register | 16 | R/W    |

| 0x0A                          | SEQCONT   | Sequencer Control Register    | 16 | R/W    |

| 0x0C                          | SEQSTAT   | Sequencer Status Register     | 16 | R/W    |

| 0x0E                          | SEQTIMER  | Sequencer Timer Register      | 16 | R/W    |

| 0x10                          | -         | Reserved                      | -  | -      |

|                               |           |                               |    |        |

| 0x7F                          | -         | Reserved                      | -  | -      |

| 0x80-BE                       | SIRAM0-31 | Sequencer Instruction RAM     | 16 | R/W    |

| 0xC0-FE                       | SDRAM0-31 | Sequencer Data RAM            | 16 | R      |

Table 3-2 : Local Register Address Space

## 3.2.1 ADC Control Register CONTREG (Offset 0x00)

The ADC Control Register CONTREG is used to select the input channel, gain and mode for the next data conversion.

If "Sequencer Mode" is selected (SEQCONT register bit 0 set to '1') write access to the ADC Control Register CONTREG is ignored.

| Bit   | Symbol    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Access | Reset<br>Value |

|-------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|

| 15:11 |           | Write: Don't care<br>Read: Always '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |        | 0              |

| 10    | INTENA    | Interrupt Request Enable<br>0 = Disabled<br>1 = Enabled (PCI INTA line)<br>If "Automatic Settling Time Mode" is OFF, an interrupt request is<br>generated<br>a) when the settling time is done, and<br>b) when the conversion is done and data is valid in the<br>DATAREG register.<br>If "Automatic Settling Time Mode" is ON, an interrupt is<br>generated when the conversion is done and data is valid in the<br>DATAREG register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R/W    | 0              |

| 9     | PIPL      | <ul> <li>Pipeline Mode Control</li> <li>0 = OFF</li> <li>Data conversion (n) is shifted into the DATAREG register after the conversion (n) is done.</li> <li>1 = ON</li> <li>Data conversion (n-1) is shifted into the DATATREG register during the conversion (n).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R/W    | 0              |

| 8     | Automatic | <ul> <li>Automatic Settling Time Mode Control</li> <li>0 = OFF (Normal Mode)</li> <li>The conversion setup is configured by the write to the CONTREG register with this bit cleared.</li> <li>The SETTL_BUSY bit in the STATREG register must be read as '0' before a conversion is started.</li> <li>A conversion is started by a write to the CONVERT register.</li> <li>After a conversion has been started, the next conversion may be setup by writing again to the CONTREG register.</li> <li>Reading the ADC_BUSY bit in the STATREG register as '0' indicates valid conversion data in the DATAREG register.</li> <li>1 = ON (Automatic Mode)</li> <li>The data conversion is initiated by a write to the CONTREG register where this bit is set. The data conversion is automatically started when the settling time is done.</li> <li>Reading the ADC_BUSY bit in the STATREG register as '0' indicates valid conversion data in the DATAREG register as '0' indicates valid conversion is initiated by a write to the CONTREG register where this bit is set. The data conversion is automatically started when the settling time is done.</li> <li>Reading the ADC_BUSY bit in the STATREG register as '0' indicates valid conversion data in the DATAREG register.</li> </ul> | R/W    | 0              |

| Bit | Symbol  |              |           |                      | Descriptio           | n                         |    | Access | Reset<br>Value |

|-----|---------|--------------|-----------|----------------------|----------------------|---------------------------|----|--------|----------------|

| 7:6 | G[1:0]  | Gain S       | Selectio  | n (Analo             | og Input Amplifier)  |                           |    | R/W    | 00             |

|     |         | G1           | G0        |                      | Gain Factor          | Input Voltage Bang        |    |        |                |

|     |         |              | GU        |                      | TPMC501 -10          | Input Voltage Range       |    |        |                |

|     |         | 0            | 0         |                      | 1                    | ±10V                      |    |        |                |

|     |         | 0            | 1         |                      | 2                    | ±10V<br>±5V               |    |        |                |

|     |         | 1            | 0         |                      | 5                    | ±3V<br>±2V                |    |        |                |

|     |         |              |           |                      | 10                   |                           |    |        |                |

|     |         | 1            | 1         |                      | TPMC501 -11          | ±1V                       |    |        |                |

|     |         | 0            | 0         |                      | 1                    | ±10V                      |    |        |                |

|     |         | 0            | 1         |                      | 2                    | ±5V                       |    |        |                |

|     |         |              | 0         |                      | 4                    |                           |    |        |                |

|     |         |              |           |                      | 8                    | ±2.50V                    |    |        |                |

|     |         | 1            | 1         |                      | o<br>TPMC501 -12     | ±1.25V                    |    |        |                |

|     |         |              | 0         |                      |                      | 0 to 10V                  |    |        |                |

|     |         | 0            | 1         |                      | 2                    | 0 to 5V                   |    |        |                |

|     |         |              | 0         |                      | 5                    | 0 to 3V                   |    |        |                |

|     |         |              | 1         |                      | 10                   | 0 to 2V                   |    |        |                |

|     |         |              |           |                      | TPMC501 -13          |                           |    |        |                |

|     |         | 0            | 0         |                      | 1                    | 0 to 10V                  |    |        |                |

|     |         | 0            | 1         |                      | 2                    | 0 to 5V                   |    |        |                |

|     |         | 1            | 0         |                      | 4                    | 0 to 2.50V                |    |        |                |

|     |         | 1            | 1         |                      | 8                    | 0 to 1.25V                |    |        |                |

|     |         |              | 1 1       |                      |                      |                           |    |        |                |

| 5   | SE/DIFF | -            |           |                      | de Control           |                           |    | R/W    | 0              |

|     |         |              |           | nded mo              | channels are avail   | ahle                      |    |        |                |

|     |         |              |           | al mode              |                      |                           |    |        |                |

|     |         | 16           | 6 differe | ntial ch             | annels 1 to 16 are   | available, channels 17 to | 32 |        |                |

|     |         |              |           | as - inp<br>oossible | ut for channels 1 to | o 16.                     |    |        |                |

| 4:0 | CS[4:0] |              |           |                      | og Input Channel)    |                           |    | R/W    | 00000          |

|     | 00[]    | <b>C</b> nam |           |                      |                      |                           |    |        |                |

|     |         |              | CS        | 4:0]                 | Single-ended         | Differential              |    |        |                |

|     |         |              |           |                      | Channel              | Channel                   |    |        |                |

|     |         |              |           |                      | SE/DIFF = 0          | SE/DIFF = 1               |    |        |                |

|     |         |              | 000       | 000                  | CH1                  | CH1                       |    |        |                |

|     |         |              | L         |                      |                      |                           |    |        |                |

|     |         |              | 01        | 111                  | CH16                 | CH16                      |    |        |                |

|     |         |              | <u> </u>  |                      |                      | N/A                       |    |        |                |

|     |         |              | 11        | 111                  | CH32                 | N/A                       |    |        |                |

## 3.2.2 ADC Data Register DATAREG (Offset 0x02)

| Bit  | Symbol | Description                  | Access | Reset<br>Value |

|------|--------|------------------------------|--------|----------------|

| 15:0 | DATA   | Converted Digital Data Value | R      | 0              |

Table 3-4 : 16 bit ADC Data Register DATAREG

The 16 bit data value allows direct data processing as 16 bit binary two's complement integer values.

The content of the ADC Data Register DATAREG is not valid as long as the ADC\_BUSY bit in the ADC Status Register STATREG is set.

| Analog Input Voltage | Digital Value<br>TPMC501 Option<br>-10 / -20, -11 / -21<br>Binary two's complement | Digital Value<br>TPMC501 Option<br>-12 / -22, -13 / -23<br>Straight binary |

|----------------------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| + Full Scale – 1LSB  | 0x7FFF                                                                             | 0xFFFF                                                                     |

| Midscale             | 0x0000                                                                             | 0x8000                                                                     |

| Midscale – 1LSB      | 0xFFFF                                                                             | 0x7FFF                                                                     |

| - Full Scale         | 0x8000                                                                             | 0x0000                                                                     |

Table 3-5 : ADC Data Coding

### 3.2.3 ADC Status Register STATREG (Offset 0x04)

| Bit  | Symbol        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Access | Reset<br>Value |

|------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|

| 15:2 |               | Always read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R      | 0              |

| 1    | SETTL<br>BUSY | SETTL_BUSY<br>Indicates that the required settling time after a write to the CONTREG<br>register is not yet done.<br>If "Automatic Settling Time Mode" is OFF, this bit is set by writing to<br>the CONTREG register. The bit is cleared when the required settling<br>time is done.<br>This bit must be read as '0' before a conversion is started by a write to<br>the CONVERT register.<br>If "Automatic Settling Time Mode" is ON, this bit should be ignored. | R      | 0              |

| 0    | ADC<br>BUSY   | ADC_BUSY<br>Indicates if an actual data conversion is in progress.<br>If "Automatic Settling Time" is OFF, this bit is set by writing to the<br>CONVERT register.<br>If "Automatic Settling Time Mode" is ON, this bit is set by the write to<br>the CONTREG register.<br>This bit must be read as '0' before the conversion data is read from the<br>DATAREG register.                                                                                            | R      | 0              |

Table 3-6 : ADC Status Register STATREG

### 3.2.4 ADC Convert Register CONVERT (Offset 0x06)

The ADC Convert Register CONVERT is a 16 bit wide write only register. The ADC Convert Register is used to start an ADC conversion when "Automatic Settling Time Mode" is OFF. The user must read the SETTL\_BUSY bit in the ADC Status Register as '0' before the conversion is started. The ADC\_BUSY bit in the ADC Status Register indicates if the conversion data in the ADC Data Register is valid (ADC\_BUSY bit = '0').

It is allowed to set up a new channel/gain by writing to the ADC Control Register CONTREG immediately after starting an ADC conversion.

If "Sequencer Mode" is selected (SEQCONT register bit 0 is set to '1') write access to the ADC Convert Register CONVERT is ignored.

After power up the ADC is in a random state and requires two dummy conversions before operating correctly. This is based on the chip design of the ADC. All drivers from TEWS TECHNOLOGIES already include these two dummy conversions.

## 3.2.5 Interrupt Status Register INTSTAT (Offset 0x08)

| Bit  | Symbol         | Description                                                                                                                                                                                                                                                                                                                                                        | Access | Reset<br>Value |

|------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|

| 15:3 |                | Always read as '0'                                                                                                                                                                                                                                                                                                                                                 | R      | 0              |

| 2    | SEQ INT        | Sequencer Interrupt Pending Flag (bit is controlled by the sequencer logic)<br>If sequencer interrupts are enabled (SEQCONT register bit 1 set to '1') and a sequencer interrupt is pending (any of the SEQSTAT register bits [3:1] is '1') the sequencer interrupt pending flag is read as '1'.                                                                   | R      | 0              |

|      |                | The interrupt is cleared by writing '1' to the corresponding status bits in the SEQSTAT register.                                                                                                                                                                                                                                                                  |        |                |

| 1    | SETTL<br>READY | SETTL_READY Interrupt Flag (bit is controlled by the settling time<br>controller)<br>If interrupts are enabled (CONTREG register bit 10 is set to '1') and<br>"Automatic Settling Time Mode" is OFF (CONTREG register bit 8 is<br>set to '0') this interrupt is generated, when the settling time is done.<br>The interrupt is cleared by writing '1' to this bit. | R/C    | 0              |

| 0    | ADC<br>READY   | ADC_READY Interrupt Flag (bit is controlled by the ADC controller)<br>If interrupts are enabled (CONTREG register bit 10 is set to '1') this<br>interrupt is generated, when a data conversion is done.<br>The interrupt is cleared by writing '1' to this bit.                                                                                                    | R/C    | 0              |

Table 3-7 : Interrupt Status Register INTSTAT

## 3.2.6 Sequencer Control Register SEQCONT (Offset 0x0A)

| Bit  | Symbol         | Description                                                                                                                                                                                                                                               | Access | Reset<br>Value |

|------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|

| 15:2 |                | Always read as '0'.                                                                                                                                                                                                                                       | R/W    | 0              |

| 1    | SEQ<br>INT ENA | Sequencer Interrupts Enable Control<br>0 = Sequencer Interrupts disabled<br>1 = Sequencer Interrupts enabled (PCI INTA)<br>An interrupt request will be generated if any bit is set in the<br>SEQSTAT register (sequencer data valid or sequencer error). | R/W    | 0              |

| 0    | SEQ ON         | Sequencer Start / Stop Control<br>0 = Stops the sequencer after the last instruction<br>1 = Starts the sequencer immediately                                                                                                                              | R/W    | 0              |

Table 3-8 : Sequencer Control Register SEQCONT

## 3.2.7 Sequencer Status Register SEQSTAT (Offset 0x0C)

| Bit  | Symbol           | Description                                                                                                                                                                                                                                                                                                                                                                           | Access | Reset<br>Value |

|------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|

| 15:4 |                  | Always read as '0'.                                                                                                                                                                                                                                                                                                                                                                   | R      | 0              |

| 3    | I-RAM<br>ERROR   | Instruction RAM Error Flag<br>Set by the sequencer if the sequencer has been started and there is<br>no correct instruction in the Instruction RAM.<br>To clear this flag the user must write '1' to this bit.                                                                                                                                                                        | R/C    | 0              |

| 2    | TIMER<br>ERROR   | Time Error Flag<br>Set by the sequencer if the sequencer timer expires but the actual<br>sequence is still in progress.<br>To clear the Timer Error Flag the user must write '1' to this bit.<br>If the Sequencer Timer Register is 0 (Sequencer Continuous Mode)<br>the Timer Error Flag always read as '0'.                                                                         | R/C    | 0              |

| 1    | DATA OF<br>ERROR | Data Overflow Error Flag<br>Set by the sequencer if the last sequencer instruction is done and<br>the Data Available Flag of the previous sequence has not yet been<br>cleared by the user.<br>To clear the error flag the user must write '1' to this bit.<br>If the Sequencer Timer Register is '0' (Sequencer Continuous Mode)<br>the Data Overflow Error Flag always read as '0'. | R/C    | 0              |

| 0    | DATA AV          | Data Available Flag<br>Set if a sequence is done and new ADC data is available in the ADC<br>Data RAM.<br>After reading the ADC Data RAM the user must clear the data<br>Available Flag by writing '1' to this bit.                                                                                                                                                                   | R/C    | 0              |

Table 3-9 : Sequencer Status Register SEQSTAT

As long as any of the bits [3:1] (error flags) of the Sequencer Status Register SEQSTAT is read as '1', the sequencer will be stopped after the last instruction. The user must clear the status bit and start the sequencer again.

### 3.2.8 Sequencer Timer Register SEQTIMER (Offset 0x0E)

The Sequencer Timer Register SEQTIMER is a 16 bit wide read/write register.

The Sequence Timer is programmable from 100µs to 6.5535s in 100µs steps.

Whenever the timer reaches the programmed value the sequencer starts a new sequence with the first instruction found in the instruction RAM.

The sequencer timer value must be chosen so that the set up sequence completes before the sequencer timer expires. If the sequence timer expires while a sequence is still in progress a timer error will be asserted.

$$Value \ge \frac{12\mu s + 14.5\mu s \cdot Number \_of \_selected \_Channels}{100\mu s} + 1$$

Figure 3-1: Sequencer Timer Value

If the Sequencer Timer Register is set to '0' the "Sequencer Continuous Mode" is selected and the sequencer will start again with the first instruction of the sequence immediately after the last instruction of the previous sequence has been completed.

## 3.2.9 Sequencer Instruction RAM SIRAM0-31 (Offset 0x80 to 0xBE)

The Sequencer Instruction RAM is a 32 x 16 bit wide RAM.

Each ADC channel has its own sequencer instruction word.

| Offset to PCI<br>Base Address | Channel (Instruction) | Size (Bit) |

|-------------------------------|-----------------------|------------|

| 0x80                          | CH1 SEQ Instruction   | 16         |

| 0x82                          | CH2 SEQ Instruction   | 16         |

|                               |                       |            |

| 0xBC                          | CH31 SEQ Instruction  | 16         |

| 0xBE                          | CH32 SEQ Instruction  | 16         |

Table 3-10: Sequencer Instruction RAM SIRAM0-31

| Bit  | Symbol  | Descr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | iption                                                            |                                                                                                                                                                                                                                      |                     | Access | Reset Value |

|------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------|-------------|

| 15:4 |         | Write:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Don't                                                             | care / Read: Always '0'                                                                                                                                                                                                              |                     | R/W    | 0           |

| 3    | Enable  | 0 = S<br>1 = S<br>da<br>Examp<br>enable<br>chann                                                                                                                                                                                                                                                                                                                                                                                                                                                           | equend<br>equend<br>ata in th<br>ple: If c<br>ed, only<br>el 2 an | DC Channel for the Seque<br>cer will pass over the ADC<br>cer converts the ADC char<br>ne Sequencer Data RAM a<br>only channel 1, channel 2 a<br>y the three ADC RAM loca<br>d channel 8 are updated a<br>st only read these three A | R/W                 | 0      |             |

| 2:1  | G[1:0]  | Gain S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Selectio                                                          | on (Analog Input Amplifier)                                                                                                                                                                                                          |                     | R/W    | 00          |

|      |         | G1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | G0                                                                | Gain Factor                                                                                                                                                                                                                          | Input Voltage Range |        |             |

|      |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                   | TPMC501 -10 /                                                                                                                                                                                                                        | -20                 |        |             |

|      |         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0                                                                 | 1                                                                                                                                                                                                                                    | ±10V                |        |             |

|      |         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1                                                                 | 2                                                                                                                                                                                                                                    | ±5V                 |        |             |

|      |         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0                                                                 | 5                                                                                                                                                                                                                                    | ±2V                 |        |             |

|      |         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1                                                                 | 10                                                                                                                                                                                                                                   | ±1V                 |        |             |

|      |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                   | TPMC501 -11 /                                                                                                                                                                                                                        | -21                 |        |             |

|      |         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0                                                                 | 1                                                                                                                                                                                                                                    | ±10V                |        |             |

|      |         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1                                                                 | 2                                                                                                                                                                                                                                    | ±5V                 |        |             |

|      |         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0                                                                 | 4                                                                                                                                                                                                                                    | ±2.50V              |        |             |

|      |         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1                                                                 | 8                                                                                                                                                                                                                                    | ±1.25V              |        |             |

|      |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                   | TPMC501 -12 /                                                                                                                                                                                                                        | -22                 |        |             |

|      |         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0                                                                 | 1                                                                                                                                                                                                                                    | 0 to 10V            |        |             |

|      |         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1                                                                 | 2                                                                                                                                                                                                                                    | 0 to 5V             |        |             |

|      |         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0                                                                 | 5                                                                                                                                                                                                                                    | 0 to 2V             |        |             |

|      |         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1                                                                 | 10                                                                                                                                                                                                                                   | 0 to 1V             |        |             |

|      |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                   | TPMC501 -13 /                                                                                                                                                                                                                        |                     |        |             |

|      |         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0                                                                 | 1                                                                                                                                                                                                                                    | 0 to 10V            |        |             |